# Tendencias de Uso y Diseño de Redes de Interconexión en Computadores Paralelos

14 de Abril, 2016 Universidad Complutense de Madrid

> Ramón Beivide Universidad de Cantabria

#### **Outline**

- 1. Introduction

- 2. Network Basis

- 3. System networks

- 4. On-chip networks (NoCs)

- 5. Some current research

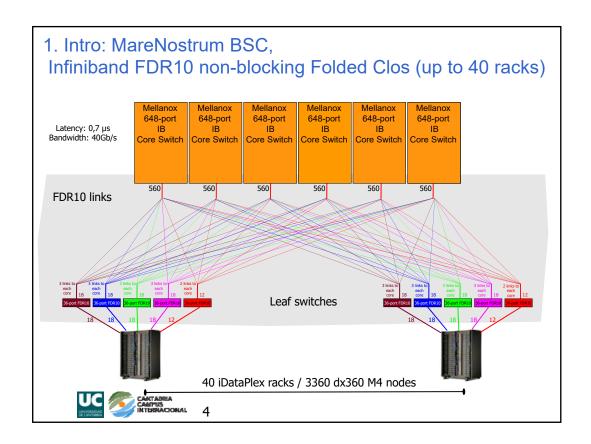

# 1. Intro: MareNostrum

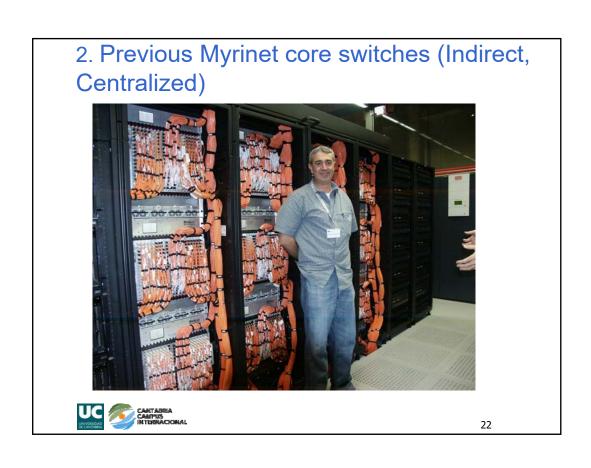

# 1. Intro: Infiniband core switches

# 1. Intro: Cost dominated by (optical) wires

# 1. Intro: Multicore E5-2670 Xeon Processor

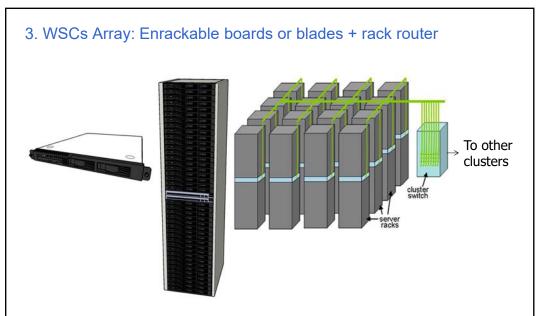

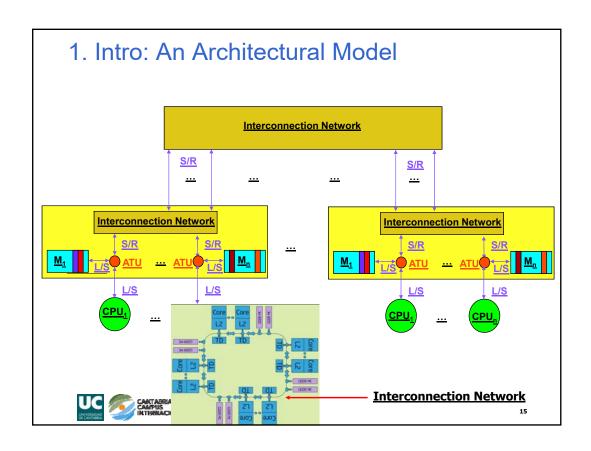

Figure 1.1: Sketch of the typical elements in warehouse-scale systems: 1U server (left), 7' rack with Ethernet switch (middle), and diagram of a small cluster with a cluster-level Ethernet switch/router (right).

- 1. Introduction

- 2. Network Basis

- Crossbars & Routers

- Direct vs Indirect Networks

- 3. System networks

- 4. On-chip networks (NoCs)

- 5. Some current research

17

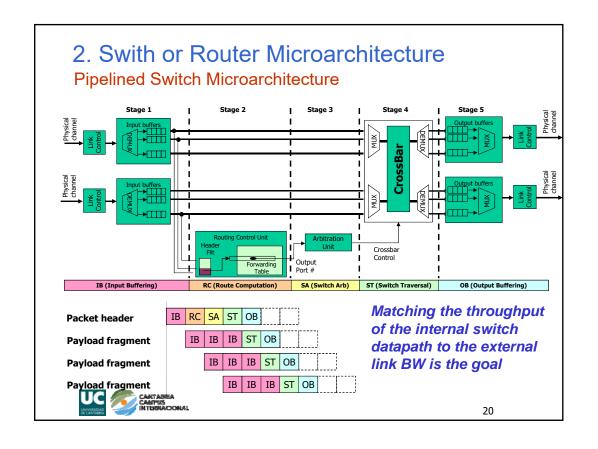

#### 2. Network Basis

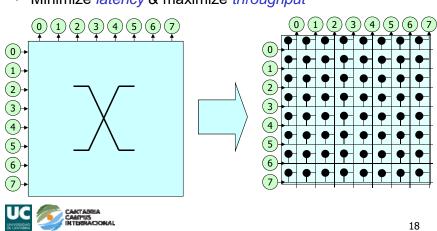

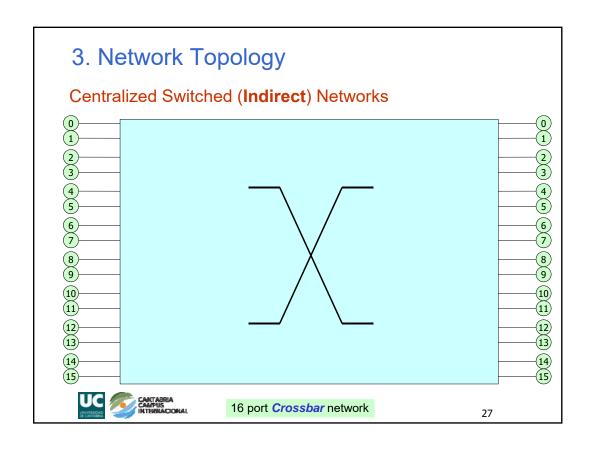

#### All networks based on Crossbar switches

- Switch complexity increases quadratically with the number of crossbar input/output ports, N, i.e., grows as O(N²)

- Has the property of being non-blocking (N! I/O permutations)

- Bidirectional for exploiting communication locality

- Minimize latency & maximize throughput

# 2. IBM BG/Q (Direct, Distributed)

23

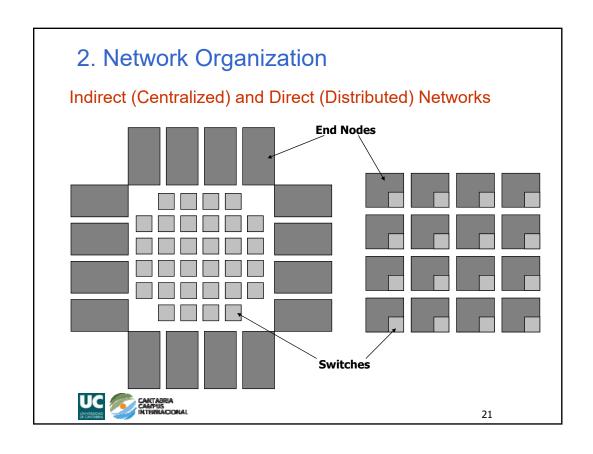

# 2. Network Organization

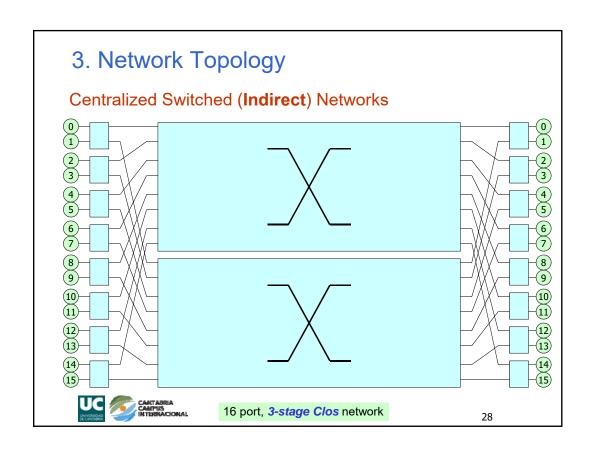

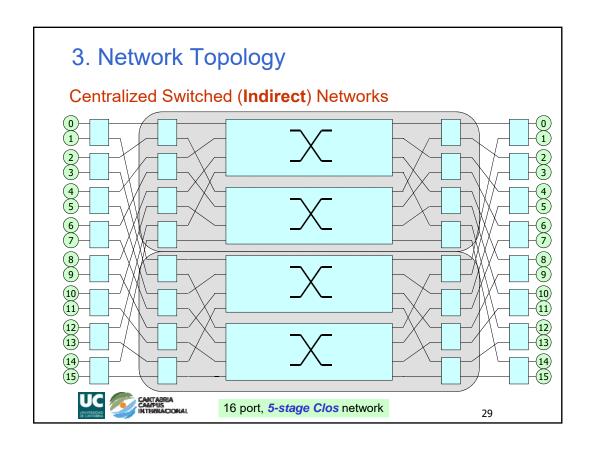

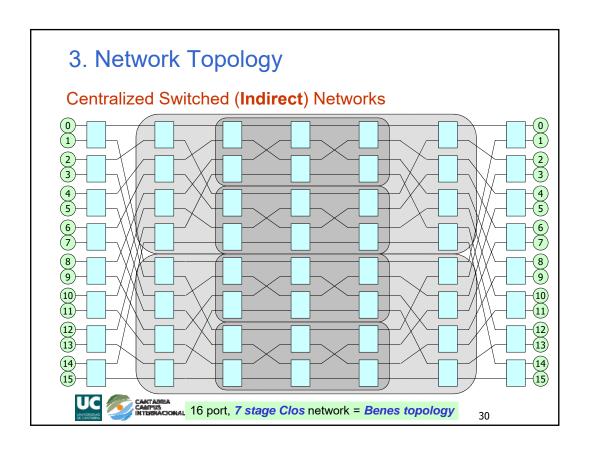

- As crossbars do not scale they need to be interconnected for servicing an increasing number of endpoints.

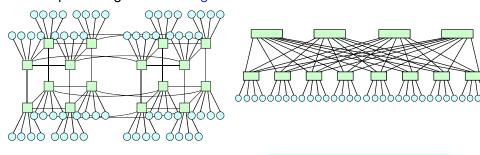

- **Direct** (Distributed) vs **Indirect** (Centralized) Networks

- Concentration can be used to reduce network costs

- "c" end nodes connect to each switch

- Allows larger systems to be built from fewer switches and links

- Requires larger switch degree

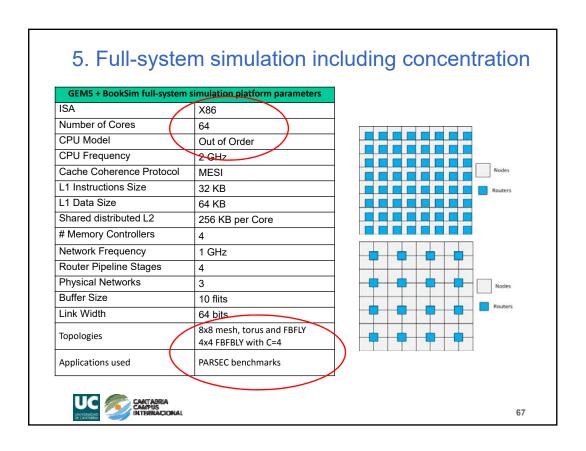

64-node system with 8-port switches, c = 4

32-node system with 8-port switches

- 1. Introduction

- 2. Network Basis

- 3. System networks

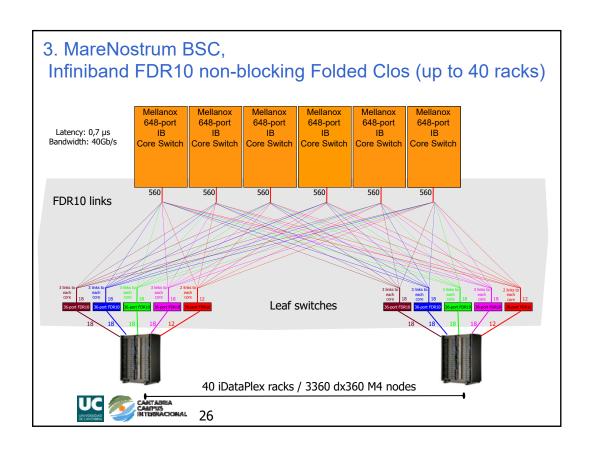

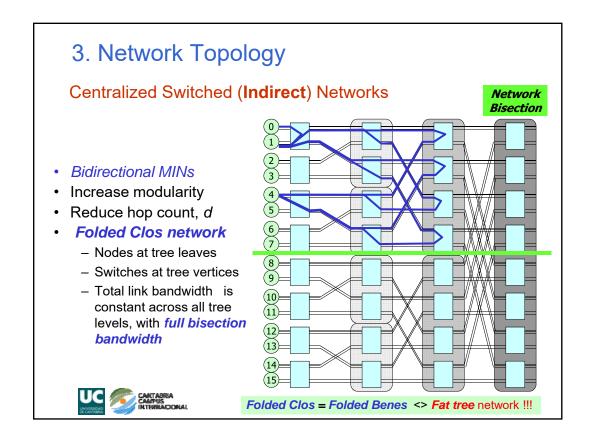

- Folded Clos

- Tori

- Dragonflies

- 4. On-chip networks (NoCs)

- 5. Some current research

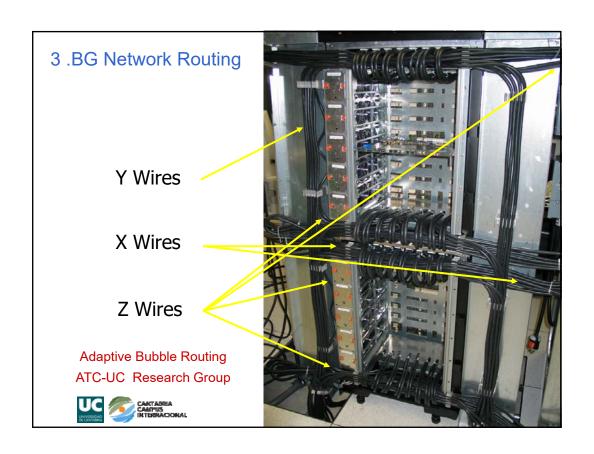

# 3. IBM BlueGene/L/P Network

Prismatic 32x32x64 Torus (mixed-radix networks) BlueGene/P: 32x32x72 in maximum configuration Mixed-radix prismatic Tori also used by Cray

CANTABRIA CAMPUS INTERNACIONAL

33

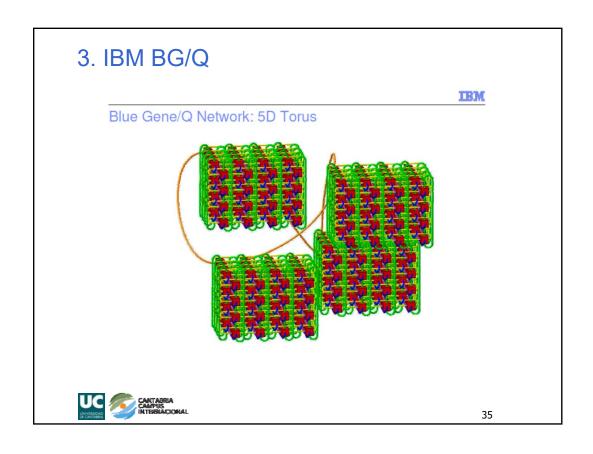

# 3. IBM BG/Q

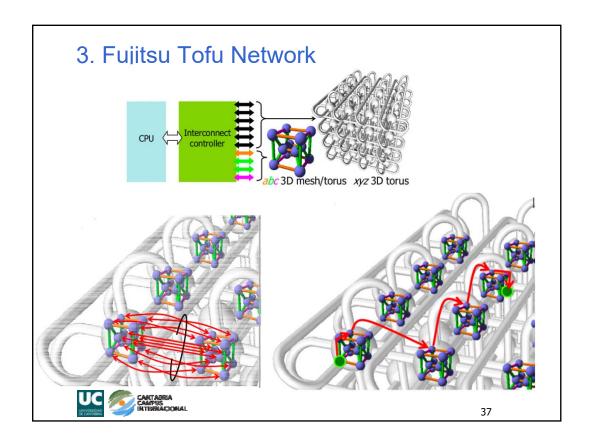

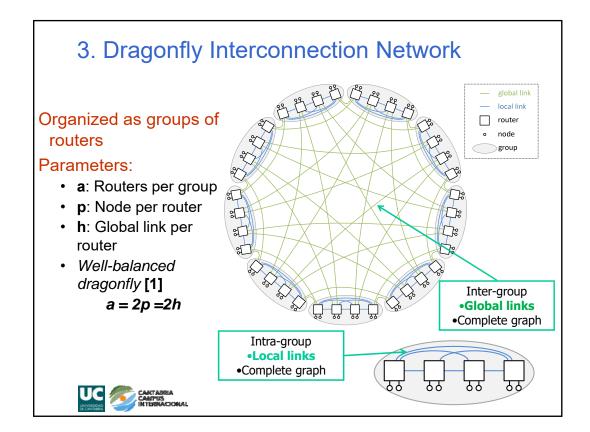

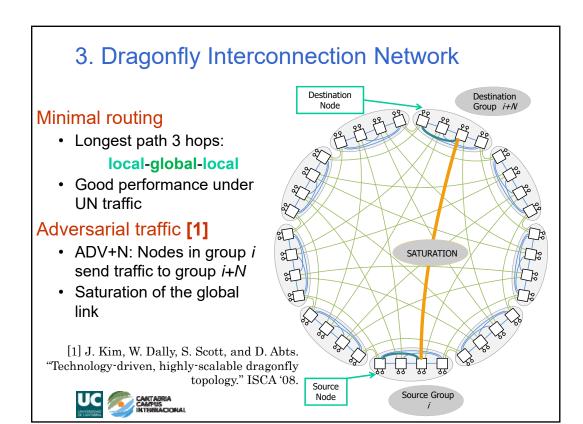

# 3. More Recent Network Topologies

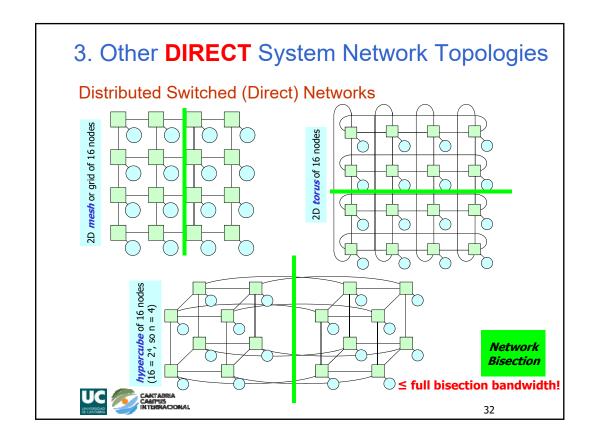

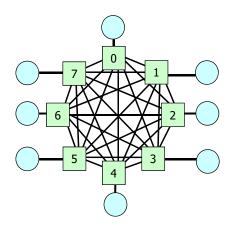

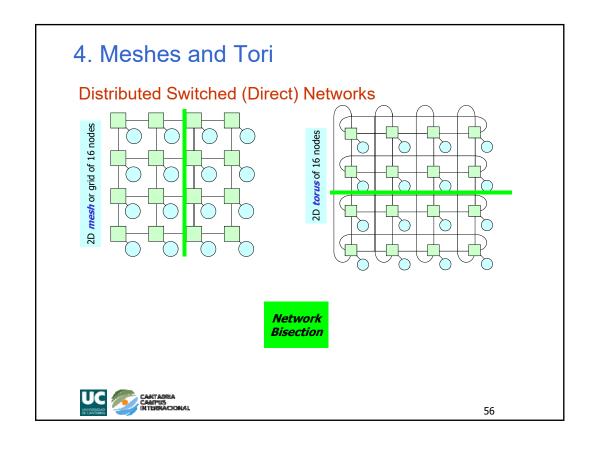

#### Distributed Switched (Direct) Networks

• Fully-connected network: all nodes are directly connected to all other nodes using bidirectional dedicated links

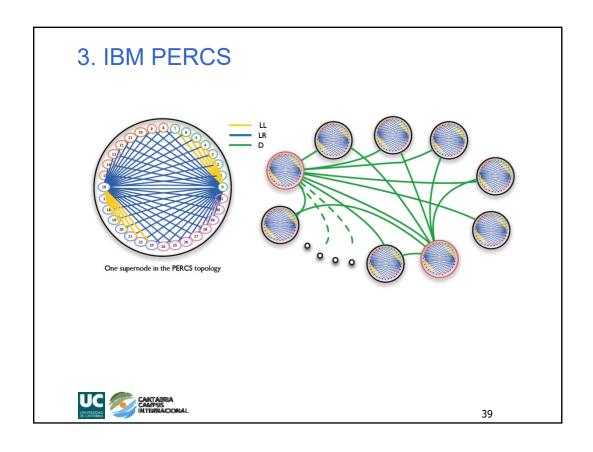

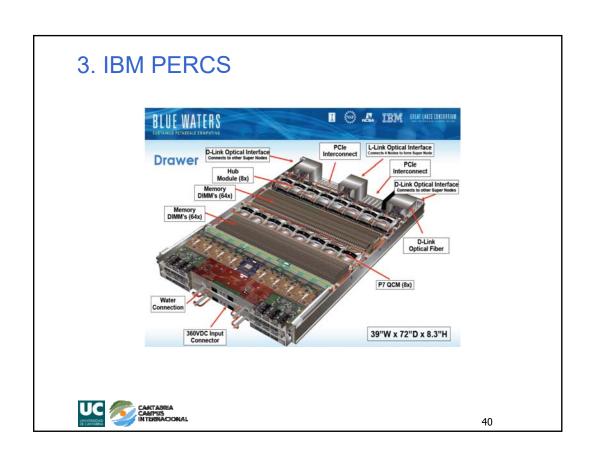

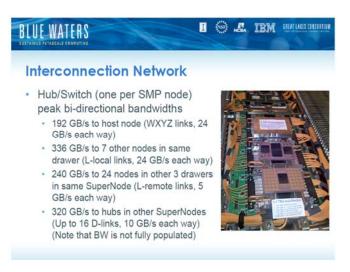

#### 3. IBM PERCS

- 1. Introduction

- 2. Network Basis

- 3. System networks

- 4. On-chip networks (NoCs)

- Rings

- Meshes

- 5. Some current research

4

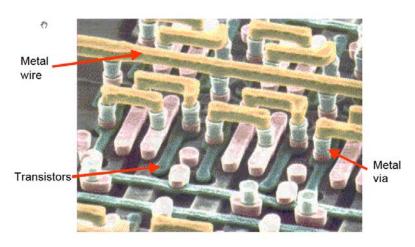

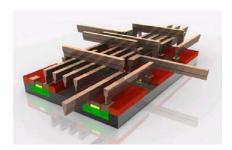

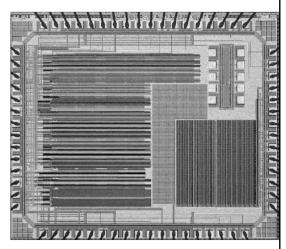

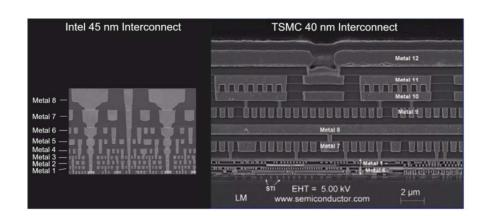

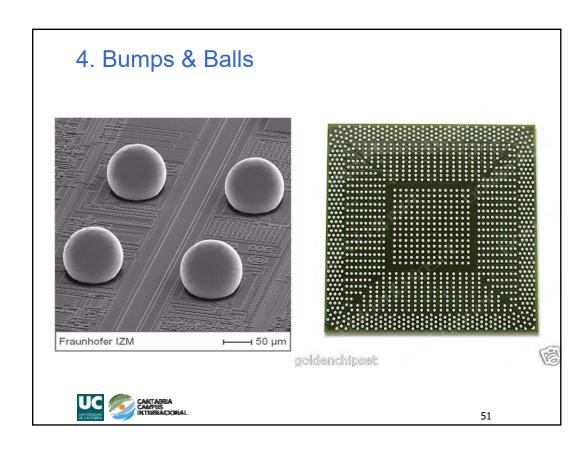

#### 4. On-Chip local interconnects

#### SEM photo of local levels interconnect

#### Global levels interconnect

# 4. Metal Layers

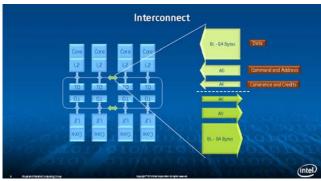

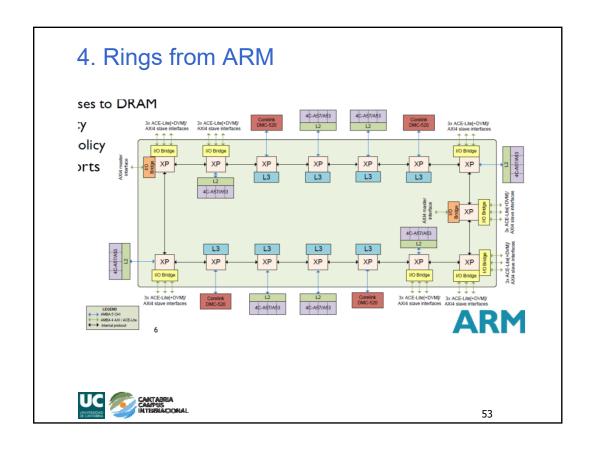

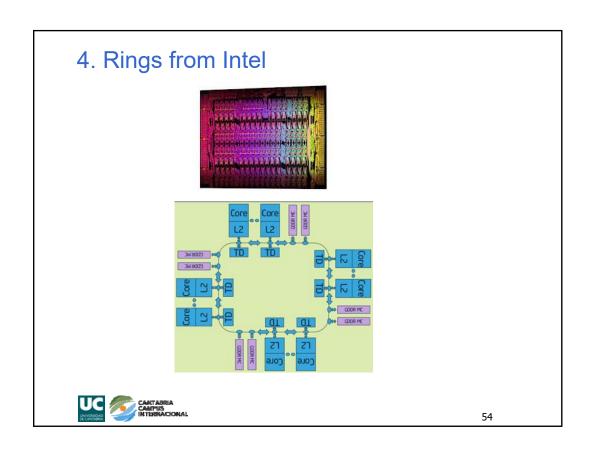

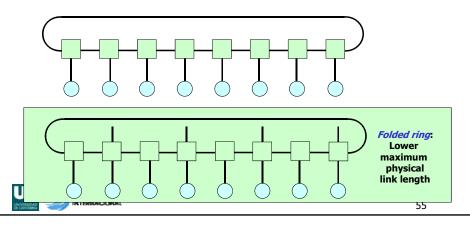

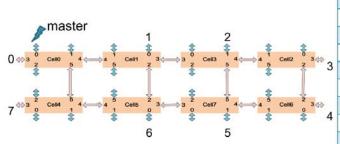

### 4. Rings (Direct or Indirect?)

- · Bidirectional Ring networks (folded)

- N switches (3 × 3) and N bidirectional network links

- Simultaneous packet transport over disjoint paths

- Packets must hop across intermediate nodes

- Shortest direction usually selected (N/4 hops, on average)

- Bisection Bandwidth???

- 6 bi-directional ports switches

- 4 physical channels for cache coherence

- 3 cycles for each hop

- 384 GB/s each cell

| Doon | Luti (o) oloo) |

|------|----------------|

| 0    | 3              |

| 1    | 6              |

| 2    | 9              |

| 3    | 12             |

| 4    | 15             |

| 5    | 12             |

| 6    | 9              |

| 7    | 6              |

| Avg. | 9              |

Lat. (cycles)

Dest.

This image was taken form the slides presented at Hot Chips 2015

#### 4. Meshes from Intel Knights Landing

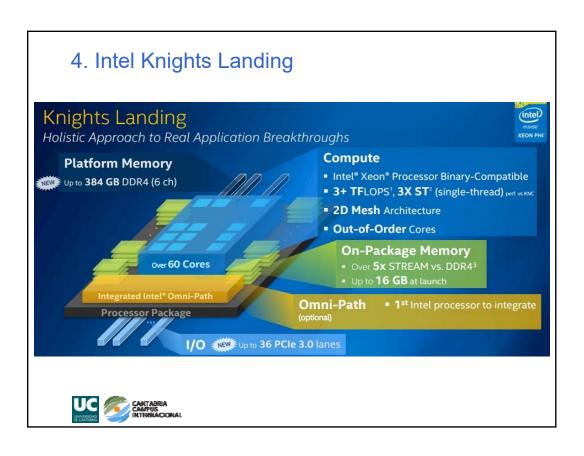

# Knights Landing: Next Intel® Xeon Phi™ Processor

Intel® Many-Core Processor targeted for HPC and Supercomputing

First self-boot Intel® Xeon Phi™ processor that is binary compatible with main line IA. Boots standard OS.

Significant improvement in scalar and vector performance

Integration of Memory on package: innovative memory architecture for high bandwidth and high capacity

Integration of Fabric on package

Three products

KNL Self-Boot KNL Self-Boot w/ Fabric

(Baseline)

(Fabric Integrated)

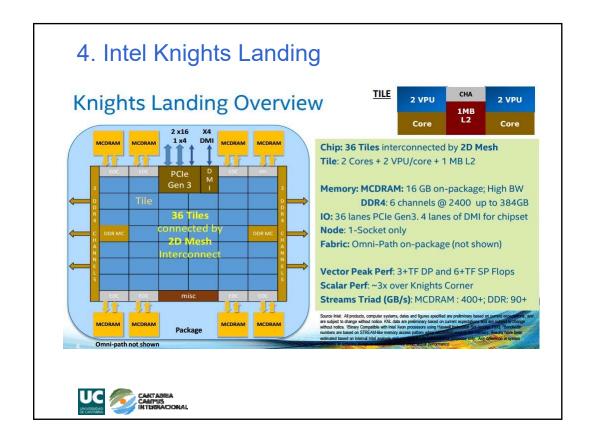

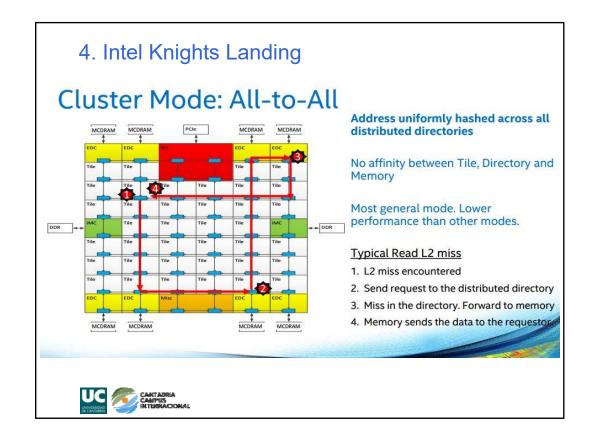

# 4. Intel Knights Landing KNL Mesh Interconnect Mesh of Rings Every row and column is a (half) ring YX routing: Go in Y → Turn → Go in X Messages arbitrate at injection and on turn Cache Coherent Interconnect MESIF protocol (F = Forward) Distributed directory to filter snoops Three Cluster Modes All-to-All (2) Quadrant (3) Sub-NUMA Clustering

- 1. Introduction

- 2. Network Basis

- 3. System networks

- 4. On-chip networks (NoCs)

- 5. Some current research

#

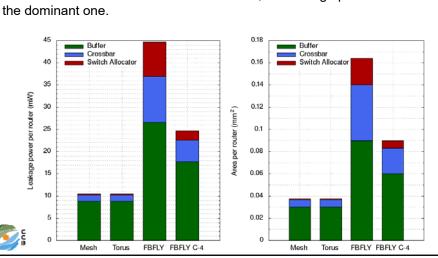

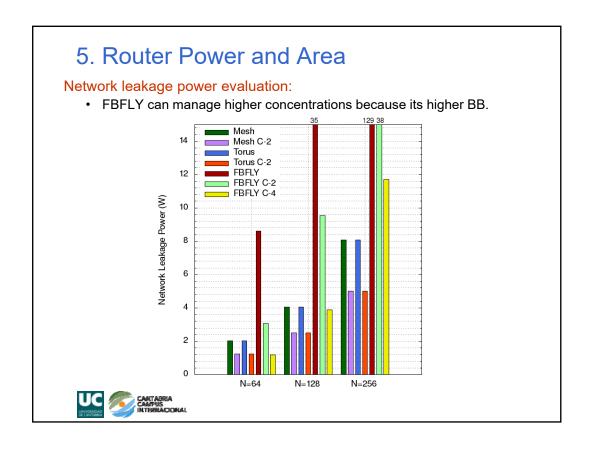

#### 5. Router Power and Area

#### Router leakage power and area evaluation:

- · Buffers are the most consuming part of the router.

- Crossbars and allocators grew quadratically with the number of ports.

- The load in these simulations is low. Hence, the leakage power is the dominant one