# lnec

# NANOSCALE CASCADED PLASMONIC LOGIC GATES FOR NON-BOOLEAN WAVE COMPUTATION FRANCKY CATTHOOR AND PLASMONICS TEAM MEMBERS

# INTRODUCTION OF PHYSICS PRINCIPLES

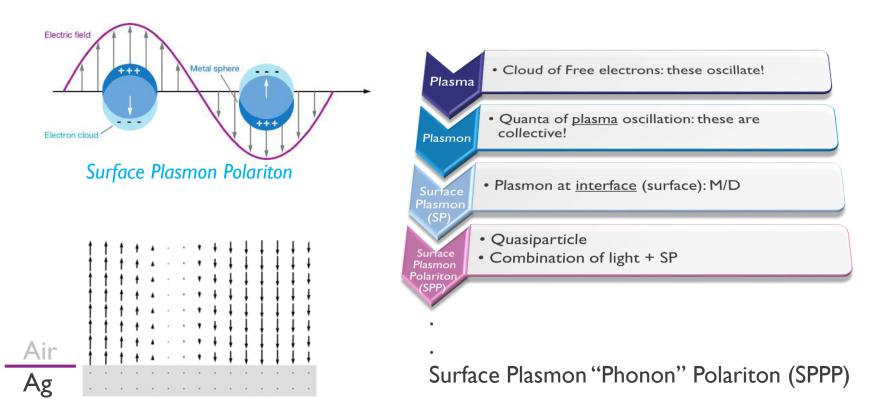

# PLASMON, SP, SPP, SPPP, ...

#### Source: wiki

© IMEC 2016-18

# WHAT IS PLASMONICS?

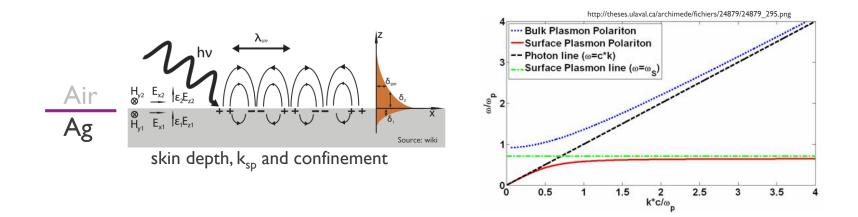

*Plasmonics* is the study of the interaction between electromagnetic field and free electrons in a metal. -wiki

For a given wavelength of excitation, SPP wavelength is smaller: <u>Squeeze Effect!</u> Optical Frequencies with a smaller wavelength: <u>light on a wire!</u>

# TEAM

## STRONG COLLABORATION WITH SEVERAL UNIV GROUPS

- IMEC: Francky Catthoor, PhD Surya Gurunarayanan, Odysseas Zografos, Dennis Lin, Pol Van Dorpe, Iuliana Radu, Bart Soree;

- Georgia Tech : PhDs Sourav Dutta, Dr. Chenyun Pan, PhD Samantha Lubaba Noor, Prof. Azad Naeemi

- EPFL: PhD Eleonora Testa, Dr. Matthias Soeken, Prof. Nanni De Micheli

- KULeuven-MICAS: PhD Kristof Dens, Prof. Patrick Reynaert

# WHICH WAVE PHENOMENON TO START FROM?

# WAVE-BASED COMPUTING MAIN CHARACTERISTICS WE WANT

- Spin waves and plasmonics have common feature wave based computing

- Phase as a state variable logic "I" and "0" encoded in the phase of the wave

- Exploit interference of the waves

- Inherent feature majority voting due to interference which provides new way

of combining boolean and non-boolean logic

But also other very non-conventional logic wave functions can be created

# INTRODUCTION TO PLASMONIC LOGIC HOW DOES WAVE COMPUTATION WORK?

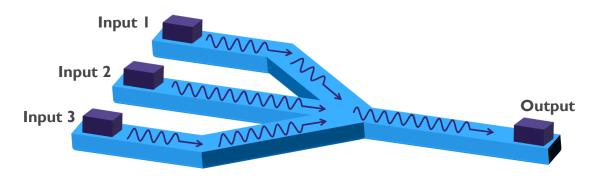

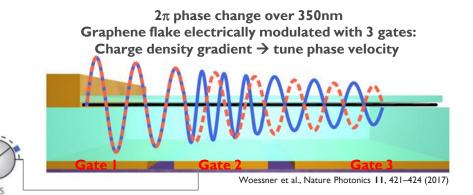

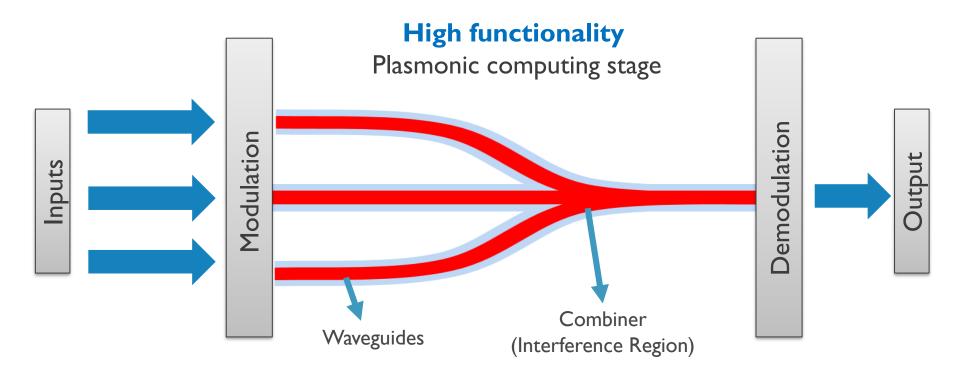

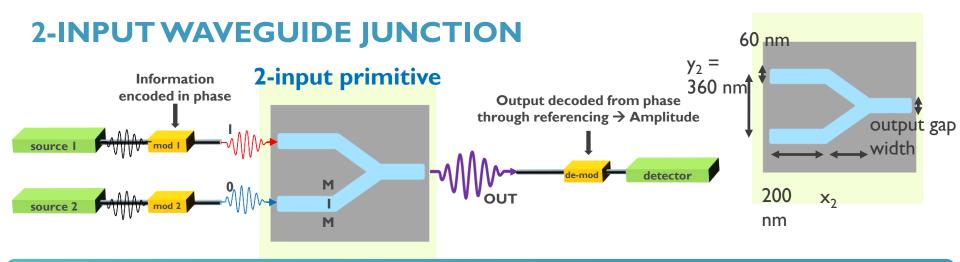

In wave computing, information is coded in the phase or the amplitude of the wave.

Computation by interference Majority logic gate

| П | 12 | 13 | 0 |

|---|----|----|---|

| 0 | 0  | 0  | 0 |

| 0 | 0  | I  | 0 |

| 0 | Ι  | I  | I |

| I | Ι  | I  | I |

Output phase after interference is equal to the majority of input phases.

## Different waves and physical state variables can be used.

ເງຍອ

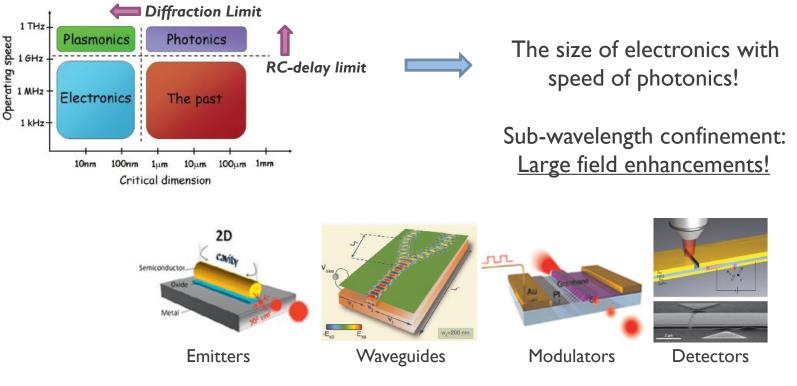

# **NEED FOR PLASMONICS**

9

# WAVE COMPUTING PARADIGMS

## COMPARISON OF MAIN OPTIONS EXPLORED

| Property        | Spin waves<br>Magnons | Plasmons        |                                                       |

|-----------------|-----------------------|-----------------|-------------------------------------------------------|

| Area/gate       | Ċ                     | $\odot$         |                                                       |

| Gate Energy     | $\odot$               | $\bigcirc$      | Overall area and                                      |

| Overhead Energy | ?                     | ?               | <ul> <li>energy per<br/>function is likely</li> </ul> |

| Delay-latency   | $\odot$               | $\odot$ $\odot$ | better with                                           |

| Throughput      | <u></u>               | $\odot$         | plasmonics                                            |

The above should be reached without going to too high speed (>>THz) in/out bottleneck that dominates everything (which happens in photonic computing!)

## ເຫາຍດ

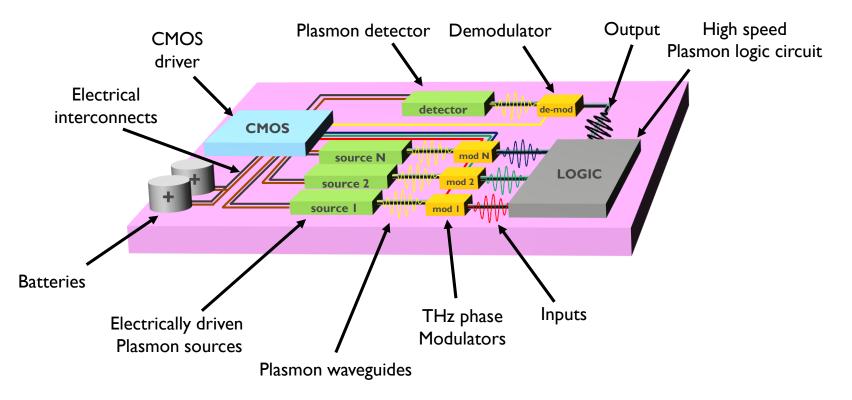

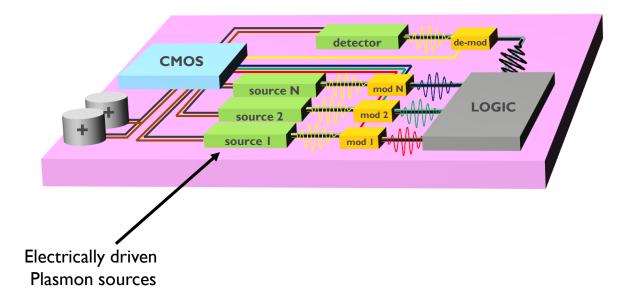

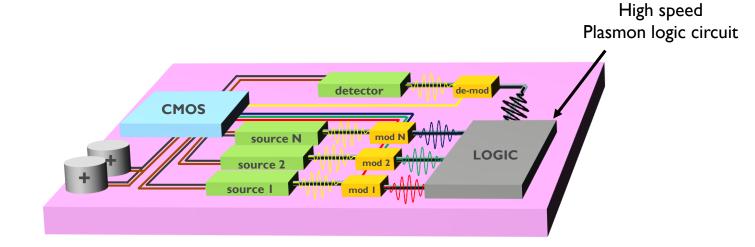

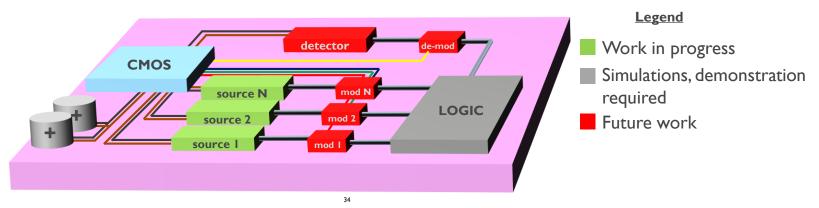

# ON-CHIP PLASMONIC LOGIC THE BIG PICTURE

### ເງຍອ

# ON-CHIP PLASMONIC LOGIC EXCITATION (PHD OF SURYA GURUNARAYANAN)

ເງຍອ

# PLASMON SOURCES

# Two types: Optical & Electrical

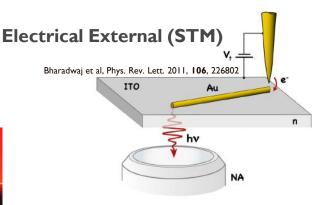

I. Laser (optical) or STM tips (electrical) Fast, but external schemes

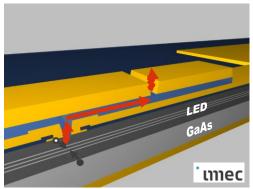

2. On-chip semiconductor based LEDs Locally emit light which excites plasmons. Recombination limited  $\rightarrow$  slow (~ns)

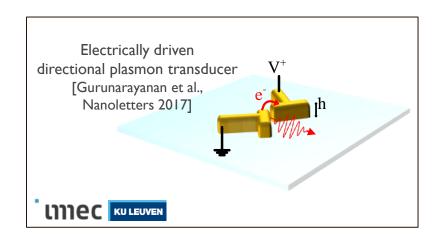

3.Tunneling:

~Instantaneous → promising

## **Optical External (Laser)**

Zhao et al., EPJ Appl. Metamat. 2014, 1, 6

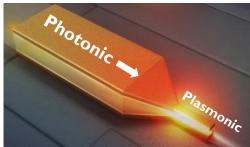

## **Optical Internal (3D taper)**

Choo et al, Nature Photonics 6, 838-844 (2012)

## **Electrical Internal (LED)**

Neutens et al, Nano Lett. 2010, 10, 1429–1432

# Tunneling is promising, need on-chip solution!

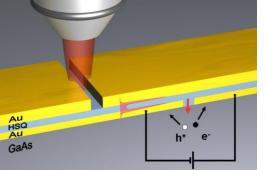

# PLASMON SOURCE (ELECTRICAL)

On-chip voltage-based directional emitter

- Actively working on on-chip plasmon source

- First working prototype designed and developed at imec.

- > Transducer from Electrical to Plasmon domain

- Ultra-fast (ps) and ultra-small (~100nm)

## **On-chip electrical plasmon source demonstrated.**

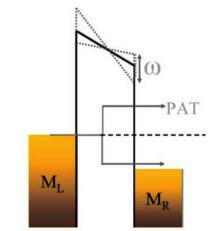

# PLASMON PHASE MODULATORS

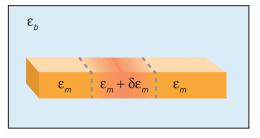

## Information encoding in the phase

Modulation of metal permittivity

$\varepsilon_{b}$

$\varepsilon_{h} + \delta \varepsilon_{h}$

$\varepsilon_{h}$

Possible schemes: Electrical, mechanical, optical or thermal

- No ultra-small solutions exist!

- Requires further research.

More research required!

# ON-CHIP PLASMONIC LOGIC THE BIG PICTURE

# WAVE COMPUTING WITH PLASMONS

Interference based ultra-fast computing

# WAVEGUIDE COMPOSITION AND MATERIAL STACK EXPLORATION

# PLASMON WAVEGUIDES

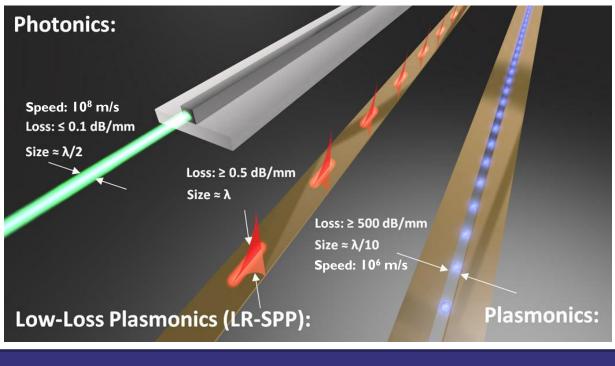

Comparison with photonic waveguide

Scale down size without compromising throughput

# PLASMON WAVEGUIDES

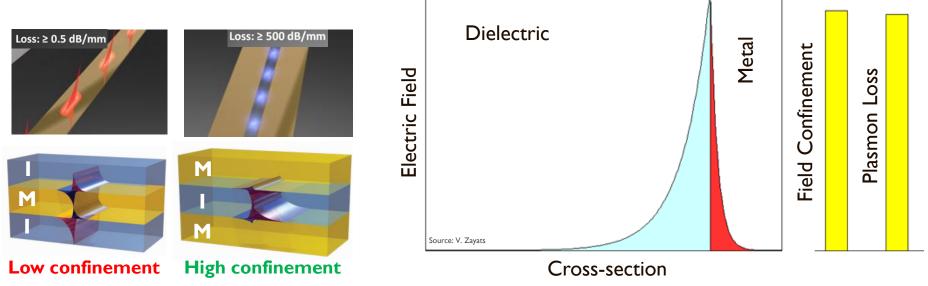

## Two basic flavors : IMI & MIM

- IMI configuration is better suited for long propagation  $\rightarrow$  plasmon interconnects

- Low confinement  $\rightarrow$  Large pitch

- MIM configuration is better suited for logic  $\rightarrow$  strong confinement  $\rightarrow$  small size  $\rightarrow$  small pitch

## MIM configuration is better suited for logic

## ເງຍອ

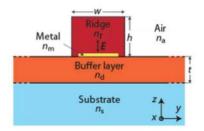

# **BASIC MATERIAL STACK FOR WAVEGUIDE: IMI**

Explore waveguide stack options concl: IMI or MIM easiest to start from

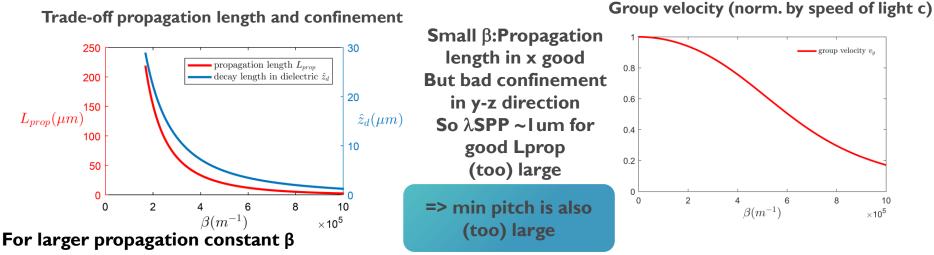

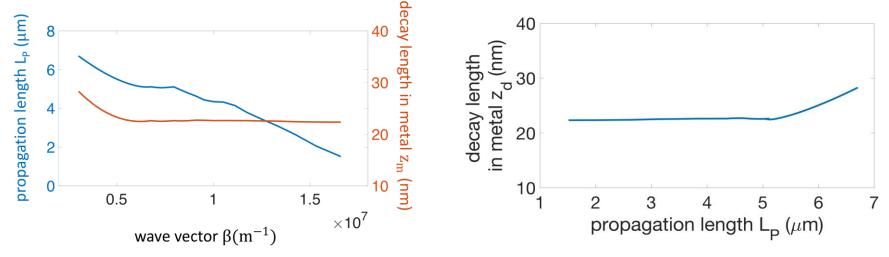

TRADE-OFF BETWEEN PROPAGATION LENGTH, CONFINEMENT AND GROUP VELOCITY IN IMI

- Better y confinement (inverse with decay length) → denser packing of wires and devices ©

- Smaller propagation length  $L_{prop} \rightarrow$  less cascading and more E loss  $\otimes$

- Lower group velocity  $v_g \rightarrow$  higher delay  $\otimes$

ເກາຍເ

Ref: MSc thesis Jonas Doevenspeck'16 and j.paper:

Design and simulation of plasmonic interference-based majority gate

AIP Advances 7, 065116 (2017); doi: <u>http://dx.doi.org/10.1063/1.4989817</u>

# **BASIC MATERIAL STACK FOR WAVEGUIDE: MIM CASE**

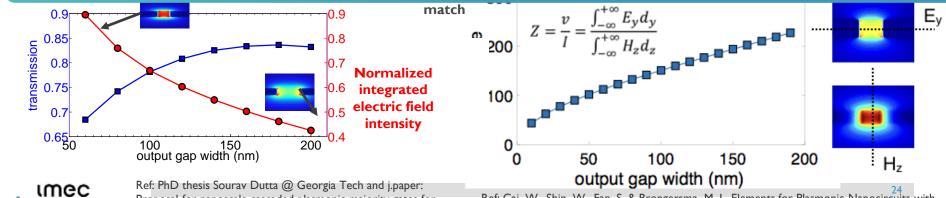

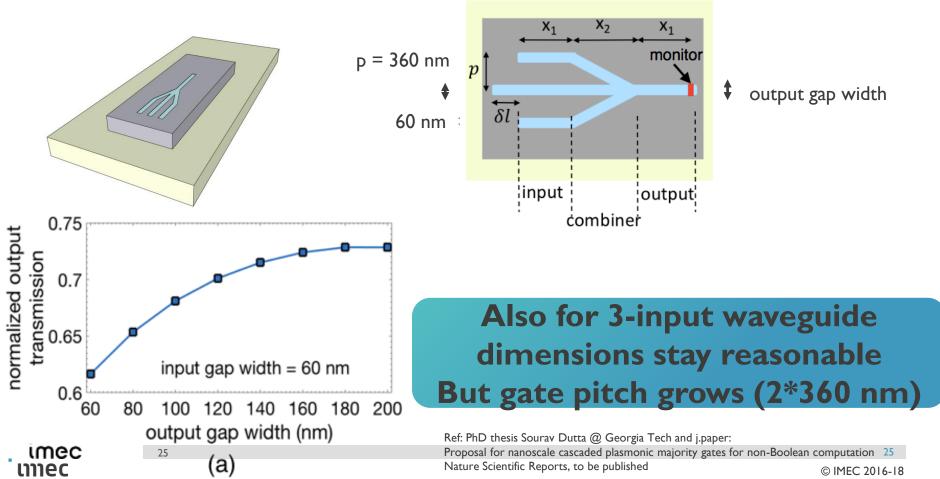

$\begin{array}{c} \mbox{Propagation length in x direction is medium (few um)} \\ \mbox{But good confinement in the y direction} \\ \mbox{Selected } \lambda \mbox{SPP} \ \mbox{~860 nm is still high but the metal sides of the} \\ \mbox{MIM waveguide determine the actual y-confinement (decay length)} \end{array}$

=> min pitch is small (100s of nm)

Ref: PhD thesis Sourav Dutta @ Georgia Tech and j.paper: Proposal for nanoscale cascaded plasmonic majority gates for non-Boolean computation

Nature Scientific Reports, to be published

# FROM MATERIAL STACK TO WAVEGUIDE JUNCTION AND LOGIC GATE

## Trade-off between ease of detectability and transmission leads to good width/size

Ref: PhD thesis Sourav Dutta @ Georgia Tech and j.paper: Proposal for nanoscale cascaded plasmonic majority gates for non-Boolean computation. Nature Scientific Reports, to be published

ເກາຍດ

Ref: Cai, W., Shin, W., Fan, S. & Brongersma, M. L. Elements for Plasmonic Nanocircuits with Three-Dimensional Slot Waveguides. Advanced materials **22**, 5120-5124 (2016). 2016-18

# **3-INPUT LOGIC GATE**

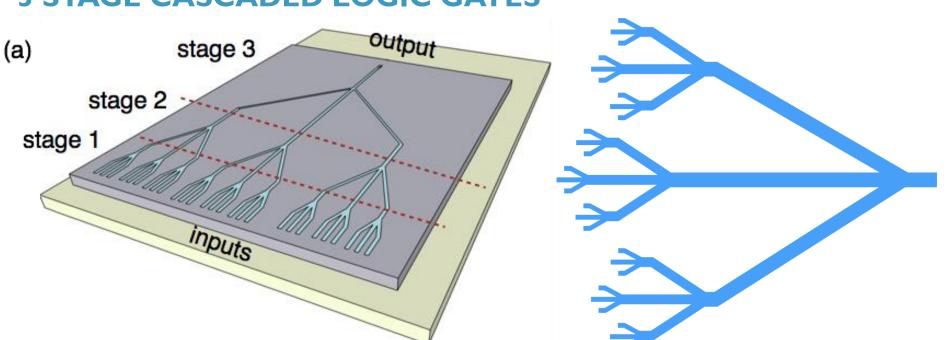

# CASCADING STAGES TO CREATE RELEVANT CIRCUITS

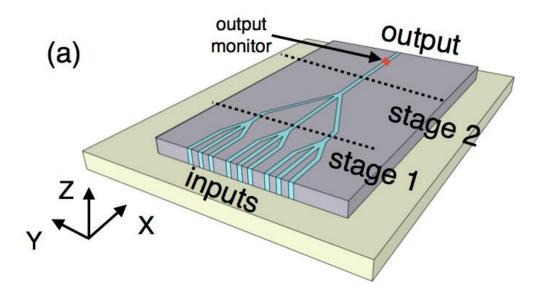

# **2 STAGE CASCADED LOGIC GATES**

# Stage I width= 60 nm Stage2 width= 120 nm

Simple way of cascading (as opposed to e.g. spin waves in earlier session)

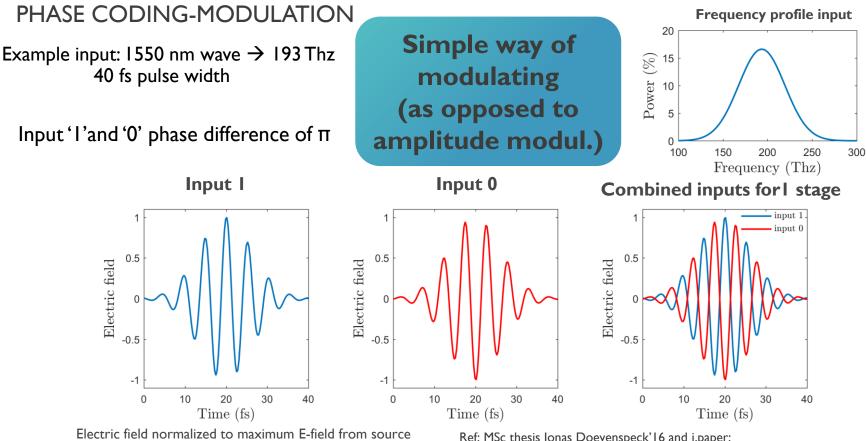

# **INPUT WAVEFORM ILLUSTRATION**

Ref: MSc thesis Jonas Doevenspeck'16 and j.paper:

Design and simulation of plasmonic interference-based majority gate

AIP Advances 7, 065116 (2017); doi: http://dx.doi.org/10.1063/1.4989817

## ເງຍອ

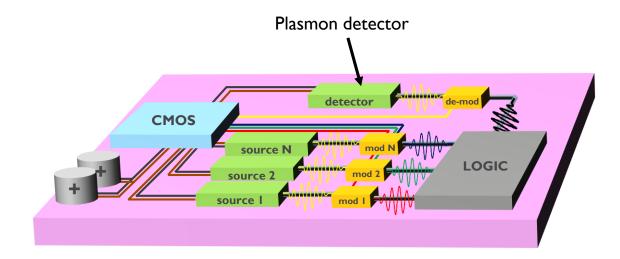

# ON-CHIP PLASMONIC LOGIC THE BIG PICTURE

## ເກາຍc

# **ON-CHIP PLASMON DETECTORS**

## Semiconductor or tunneling based

## **Semiconductors**

Plasmons

Neutens et al., Nature Photonics 3, 283-286 (2009)

I. Plasmon excites electron-hole pair in the semiconductor. 2. Carriers generate photocurrent

Drift/diffusion limited  $\rightarrow$  slow (ns to  $\mu$ s)

Falk et al., Nature Physics 5, 475-479 (2009)

nowire

Ittah et cl., NANO LETTERS 2009 Vol. 9, No. 4 1615-1620

- Oscillating field at the junction results in photon-assisted transport.

- Also works for plasmon-assisted tunneling transport

- Very fast: ~ps

## On-chip ultra-fast solution $\rightarrow$ tunneling based transducers!

Electron

Ge nanowire

30

## 2. Tunneling/Ballistic transport

# **3 STAGE CASCADED LOGIC GATES**

# Gradually widening gap/spacing but pitch remains reasonable (few um)

imec ເກາຍc

31

Ref: PhD thesis Sourav Dutta @ Georgia Tech and j.paper:

Proposal for nanoscale cascaded plasmonic majority gates for non-Boolean computation <sup>31</sup>

Nature Scientific Reports, to be published

# MAPPING OF REALISTIC CIRCUIT FUNCTIONALITY

# **REAL PROOF-OF-THE-PUDDING COMES FROM FUNCTIONS!**

- This requires access to plasmonics oriented mapping and synthesis tools because pen-and-paper/excel type studies do not incorporate the strongly non-linear and correlated nature of realistic function mapping.

- We are actively busy with this exploration in tight cooperation with EPFL and early results are promising

33

# PLASMONIC LOGIC – SUMMARY

- Very interesting results from proof-of-principle experiments:

- I. On-chip directional plasmon source is realized for the first time.

- 2. Exploration study of plasmonics waveguides supports feasibility of wave-based computing

- 3. Plasmonic Majority gate + cascadability up to 3 stages is shown.

- Challenging but exciting road ahead:

- Experimental realization of majority logic

- □ Build high-level logic design elements:

- Logic synthesis mapping

# **REMAINING CHALLENGES**

- Referencing output for changing the state variable from phase to amplitude allows realistic detection mechanism. Still requires low power THz range electronic detector but we have started investigation into that + collaboration planned

- Also need for effective low power plasmon stimulator: active exploration ongoing

- Mapping/synthesis framework should be adapted: we are actively collaborating on this

# embracing a better life